## Nonvolatile MoS<sub>2</sub> field effect transistors directly gated by single crystalline epitaxial ferroelectric

Zhongyuan Lu, Claudy Serrao, Asif Islam Khan, Long You, Justin C. Wong, Yu Ye, Hanyu Zhu, Xiang Zhang, and Sayeef Salahuddin

Citation: Appl. Phys. Lett. **111**, 023104 (2017); View online: https://doi.org/10.1063/1.4992113

View Table of Contents: http://aip.scitation.org/toc/apl/111/2

Published by the American Institute of Physics

## Articles you may be interested in

Ferroelectric transistors with monolayer molybdenum disulfide and ultra-thin aluminum-doped hafnium oxide Applied Physics Letters **111**, 013103 (2017); 10.1063/1.4991877

Stabilization of ferroelectric phase in tungsten capped Hf<sub>0.8</sub>Zr<sub>0.2</sub>O<sub>2</sub> Applied Physics Letters **111**, 022907 (2017); 10.1063/1.4993739

Strong dopant dependence of electric transport in ion-gated  $\mathsf{MoS}_2$

Applied Physics Letters 111, 013106 (2017); 10.1063/1.4992477

Four logic states of tunneling magnetoelectroresistance in ferromagnetic shape memory alloy based multiferroic tunnel junctions

Applied Physics Letters 111, 022902 (2017); 10.1063/1.4992795

Modulation-doped  $\beta$ -(Al<sub>0.2</sub>Ga<sub>0.8</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> field-effect transistor Applied Physics Letters **111**, 023502 (2017); 10.1063/1.4993569

Improvement in top-gate MoS<sub>2</sub> transistor performance due to high quality backside Al<sub>2</sub>O<sub>3</sub> layer

Applied Physics Letters 111, 032110 (2017); 10.1063/1.4995242

## Nonvolatile MoS<sub>2</sub> field effect transistors directly gated by single crystalline epitaxial ferroelectric

Zhongyuan Lu,¹ Claudy Serrao,¹ Asif Islam Khan,¹ Long You,¹ Justin C. Wong,¹ Yu Ye,² Hanyu Zhu,² Xiang Zhang,² and Sayeef Salahuddin¹,a)

<sup>1</sup>Electrical Engineering and Computer Science, University of California, Berkeley, California 94720, USA <sup>2</sup>Mechanical Engineering, University of California, Berkeley, California 94720, USA

(Received 1 May 2017; accepted 24 June 2017; published online 11 July 2017)

We demonstrate non-volatile, n-type, back-gated,  $MoS_2$  transistors, placed directly on an epitaxial grown, single crystalline,  $PbZr_{0.2}Ti_{0.8}O_3$  (PZT) ferroelectric. The transistors show decent ON current (19  $\mu$ A/ $\mu$ m), high on-off ratio (10<sup>7</sup>), and a subthreshold swing of (SS  $\sim$  92 mV/dec) with a 100 nm thick PZT layer as the back gate oxide. Importantly, the ferroelectric polarization can directly control the channel charge, showing a clear anti-clockwise hysteresis. We have self-consistently confirmed the switching of the ferroelectric and corresponding change in channel current from a direct time-dependent measurement. Our results demonstrate that it is possible to obtain transistor operation directly on polar surfaces, and therefore, it should be possible to integrate 2D electronics with single crystalline functional oxides. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4992113]

wide range of functionalities, including high speed switching, large remnant polarization and therefore long memory retention time, and also transduction to a wide range of stimuli such as pressure and temperature. However, integrating the highest performance perovskite based FE materials with conventional electronics has traditionally been challenging due to significant lattice mismatch between Si and perovskites. In this context, two dimensional (2D) semiconductors<sup>2-5</sup> could be of great interest as it is possible to transfer and place them on arbitrary substrates, and therefore, it should be possible to directly integrate them with single crystalline ferroelectrics. Unfortunately, the efforts in this direction have been stymied significantly by the interface states that appear between the polar surface of ferroelectrics and the 2D layers. In fact, these surface states have such a large density that they completely screen out the polarization charge of the ferroelectric (typically >10<sup>14</sup>/cm<sup>2</sup>), thereby decoupling the 2D layer from the ferroelectric. For example, a robust trap related hysteresis (often called the "anti-hysteresis") has been observed in multiple studies. 6-9 A real ferroelectric induced hysteresis is rare. 10-12 Similarly, the ferroelectric control of the channel charge for 2D transition metal dichalcogenides (TMDs) has proved to be significantly challenging. 13–15 While the "anti-hysteresis" due to trapping/ detrapping of interface traps have been shown to be very robust, this essentially eliminates all the functional properties offered by single crystal ferroelectrics. It has also been observed that 2D ferroelectric transistors showed no hysteresis, possibly because the ferroelectric film behaved mainly as

a high- $\kappa$  dielectric layer. <sup>16</sup> Therefore, heterostructure of single

crystal FE/2D channel materials where the transistor charac-

teristic is controlled purely by the FE charge is desirable. In

this paper, we demonstrate a N-type MoS<sub>2</sub> transistor with a

single crystalline FE back-gate by directly transferring the

Single crystalline ferroelectric (FE) materials provide a

MoS $_2$  layer on top of a single crystalline PbZr $_{0.2}$ Ti $_{0.8}$ O $_3$  (PZT) thin film. The channel charge follows the FE polarization. We show that the interface trap states have a direct correlation with the surface quality of the FE material. Importantly, the transistors made of the transferred layers on PZT show excellent current-voltage characteristic, comparable to those obtained with standard high- $\kappa$  dielectrics.

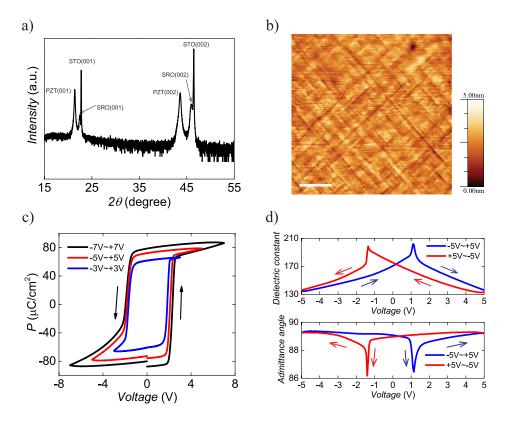

Approximately a 100 nm thick single crystalline PbZr<sub>0.2</sub> Ti<sub>0.8</sub>O<sub>3</sub> (PZT) film was grown on an epitaxially matched SrTiO<sub>3</sub> (STO) (001) substrate via KrF pulsed laser deposition (PLD). A 30 nm SrRuO<sub>3</sub> (SRO) buffer layer was used between PZT and STO as the bottom electrode of the backgate transistor structure. PZT and SRO were grown at 600 °C and 700 °C, respectively, with an oxygen background pressure of 100 mTorr. After film growth, the samples were cooled to room temperature in 1 atm oxygen at a rate of 10 °C per min. X-ray diffraction (XRD) analysis was used for phase identification [Fig. 1(a)]. Surface topography [Fig. 1(b)] was measured by atomic force microscopy (AFM). The surface RMS roughness is  $\sim 0.478 \,\mathrm{nm}$ . The polarization-voltage loops of the PZT capacitor are shown in Fig. 1(c). The permittivity vs voltage and admittance angle vs voltage behaviour are shown in Fig. 1(d). The large remnant polarization, sharp switching, and low leakage exemplified by high admittance angle indicate excellent electronic property of the synthesized film.

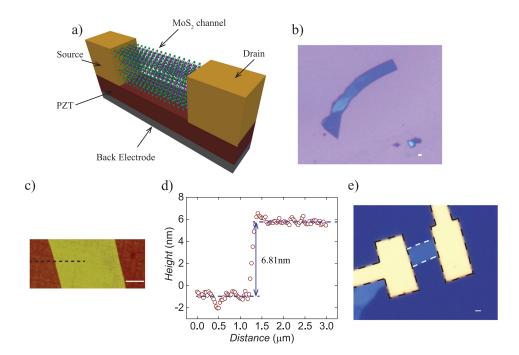

Figure 2(a) shows a schematic of the back-gate  $MoS_2$  transistor.  $MoS_2$  flakes were mechanically exfoliated from bulk crystals onto 285 nm  $SiO_2/Si$  substrates [Fig. 2(b)], which are optimal for estimating flake thickness via color contrast. Multilayer  $MoS_2$  flakes were chosen for high channel current. The selected  $MoS_2$  flakes were transferred onto PZT substrates via the dry cutting transfer process. AFM was used to measure the thickness and uniformity of the flakes after transfer. No ripples or ruptures were found as shown in Fig. 2(c). The measured thickness of the transferred flake is  $\sim$ 6.81 nm [Fig. 2(d)]. Next e-beam lithography and metal evaporation were used to pattern 100 nm of the Au

a)Email: sayeef@berkeley.edu

FIG. 1. (a) XRD pattern of the PZT/SRO/STO structure. (b) PZT film surface AFM topography. The scale bar is 1  $\mu$ m. (c) PZT film polarization-voltage loops for different voltage sweeping ranges. (d) *C-V* characteristics of the PZT film.

film as the source/drain electrodes [Fig. 2(e)]. The channel is  $3 \mu m$  in width and  $5 \mu m$  in length. After lift-off, the device was annealed at  $200\,^{\circ}\mathrm{C}$  in vacuum for 1 h to remove adsorbates from the surface and reduce the contact resistance. <sup>19,20</sup> An Agilent B1500A was used for current-voltage and current-time measurements, and all measurements were carried out in a high vacuum environment ( $2 \times 10^{-6}\mathrm{Torr}$ ). Note that we define the polarization direction as positive when it points into the channel and as negative when it points out of the channel.

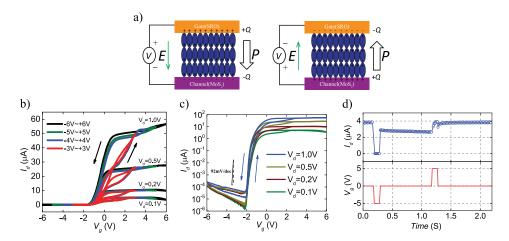

The operating principle of our ferroelectric field-effect transistor (FeFET) is depicted in Fig. 3(a). In the traditional

metal-oxide-semiconductor FET structure, applying a voltage across the gate oxide electrostatically dopes the channel via capacitive coupling. Conventional oxides can only exhibit polarization proportional to the applied voltage. In FeFETs, however, the ferroelectric maintains a remnant polarization that switches directions when an opposing electric field is applied with magnitude greater than the coercive electric field  $E_{\rm c}$ . When the polarization is pointing towards the channel, it will induce electrons in the MoS<sub>2</sub> layer, leading to a left-ward shift of the threshold voltage ( $\Delta V_{\rm t} < 0$ ); by contrast, when the polarization is pointing away from the channel, a rightward

FIG. 2. (a) Schematic of the multilayer  $MoS_2/PZT/SRO$  back-gate transistor. (b) Optical image of  $MoS_2$  flake exfoliated onto the 285 nm  $SiO_2/Si$  substrate prior to transfer. (c) AFM image of the  $MoS_2$  flake. (d) AFM result of  $MoS_2$  flake thickness. (e) Optical image of the back-gate transistor. All scale bars are  $1 \mu m$ .

FIG. 3. (a) Schematic of polarization doping in the channel with different electric field directions. (b)  $I_{\rm d}$ - $V_{\rm g}$  curves of MoS<sub>2</sub>/PZT transistor with the linear y-axis. (c)  $I_{\rm d}$ - $V_{\rm g}$  curves of the MoS<sub>2</sub>/PZT transistor with the logarithmic y-axis. (d) Time-resolved channel current changes in response to gate voltage pulse sequences.  $V_{\rm d}$ =0.1 V.

shift in the threshold voltage will ensue ( $\Delta V_t > 0$ ). Thus for an n-type transistor, a counterclockwise hysteresis is expected. The two possible polarization states can represent the "1" and "0" states in non-volatile memory. In the transistor transfer curves [Fig. 3(b)], the ON current reached as high as 19  $\mu$ A/  $\mu$ m. Current saturation and a distinct anticlockwise hysteresis window were detected at positive gate voltage. Curves in different scales are overlapping each other, showing that surface states induced by adsorbates (e.g., O2, H2O, etc.) have minimal contribution at best. For the backward direction of the gate voltage sweep, the saturation current induced by positive polarization increases with the wider sweep range. This indicates that the polarization amplitude increases with an increase in voltage across the ferroelectric. This trend is consistent with the polarization-electric field (PE) results as shown in Fig. 1(c). As shown in Fig. 3(c), the ON/OFF ratio and subthreshold swing of the transistor reached  $\sim 10^7$  and 92 mV/dec, respectively, which are comparable to those of previously reported high-quality MoS<sub>2</sub> devices.<sup>3,4</sup> Unlike conventional FeFETs, there is no forward shift in the threshold voltage  $V_t$ , implying that the negative polarization was ineffective. This is likely due to the lack of free electrons in the MoS<sub>2</sub> channel's depletion region, resulting in a weaker electric field across the ferroelectric film that is not strong enough to switch the polarization. This indicates that the observed effect of ferroelectric hysteresis is originating most likely from a partial switching of the ferroelectric. The red curves given in Fig. 3(b) indicates changes in the current direction as the gate voltage is swept from -3 V to +3 V. When the drain voltage  $V_{\rm d}$  is 1 V, the hysteresis loop is partially clockwise and partially anticlockwise. This occurs because the maximum voltage across the ferroelectric at the drain side can only reach  $V_g - V_d = 2 \text{ V}$  while the maximum voltage at the source side is  $V_g = 3$  V. Consequently, the electric field is not strong enough to switch the ferroelectric at the drain side. In contrast, when  $V_{\rm d} = 0.2 \,\rm V$ , the hysteresis loop is anticlockwise because the ferroelectric polarization state is the same at both the source and drain sides. Based on this analysis, we can conclude that the coercive voltage of the PZT film in the positive direction must be between 2.0 V and 2.8 V. This is reasonably consistent with PE measurements [Fig. 1(c)].

To test the polarization switching *in-situ*, we performed a time-resolved current measurement with a series of gate pulses. The red curve given in Fig. 3(d) indicates the

sequence of the applied gate pulses. The pulse has an amplitude of 5 V, a pulse width of  $t_{\rm on} = 100 \, \rm ms$ , and a pulse period of  $t_{\rm off} = 1$  s. The corresponding drain current is shown in the upper panel. First, a negative pulse is applied. The current goes down to very small levels but comes back up when the voltage is turned OFF. However, the current does not come up to the same level as it was before applying the pulse. This indicates that a partial switching of ferroelectric is happening in the negative direction. Next, a positive pulse is applied. The corresponding jump up in the current is clearly visible. The up directed change in current confirms the control of the channel charge by the polarization. The current is retained after the voltage is put back to zero. This shows that a robust polarization switching happens in our device in the positive direction. Together with the partial switching in the negative direction, this provides a complete memory operation for the device. Notably, the partial switching in the negative direction is expected because the channel is depleted for negative voltage, and therefore, most of the applied gate voltage drops across the channel capacitance rather than the ferroelectric. We have also performed a temperature dependent conductance measurement (see Fig. S2, supplementary material) and found that after the application of the positive voltage, the material is in the metallic phase as it would be expected from the polarity of the polarization.

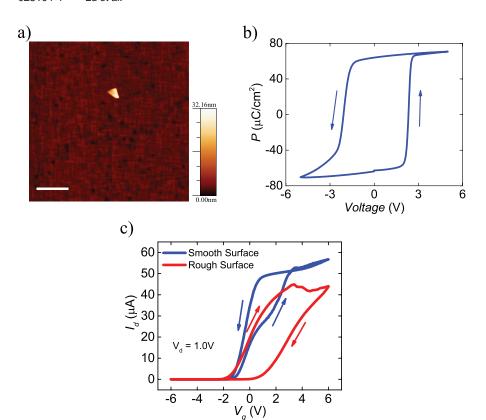

In order to understand the effect of surface roughness on the transistor behavior, we have chosen an area of the PZT sample where the surface is relatively rough [see Fig. 4(a)]. The polarization-voltage scan, as plotted in Fig. 4(b), still shows excellent ferroelectric behavior. The  $I_d$ - $V_g$  characteristic of a transistor fabricated on such a topography was measured in vacuum  $(2 \times 10^{-6} \text{Torr})$  to avoid the effects from adsorbates. Figure 4(c) directly compares the transfer curves of the MoS<sub>2</sub> ferroelectric transistors fabricated on smooth and rough surfaces, showing that transistors fabricated on rough surfaces have hysteresis loops in the clockwise direction (i.e., anti-hysteresis), similar to those results reported before, not only of MoS<sub>2</sub> but also of graphene. 6-9,13-15 Since the only difference between those two systems having different loop directions are the surface topography of PZT gate oxide layers, we postulate that a dominant reason for anti-hysteresis is interface states induced by defects on the rough surface.

Epitaxial ferroelectric films typically show excellent retention. Given that the transistors presented in this work

FIG. 4. (a) AFM topography of a rough PZT film. The scale bar is 1  $\mu$ m. (b) The polarization-electric field loop of the rough PZT film. (c) The transfer characteristics of MoS<sub>2</sub> transistors fabricated on PZT films with different surface qualities.

are back gated, the retention of the individual transistors will be determined by the film itself. However, it is important to note that in a memory array, the retention will be ultimately determined by many factors other than the film itself, including stress cycles, operating temperature, and READ disturb.

To summarize, we have fabricated n-type MoS<sub>2</sub> devices directly on single crystalline ferroelectric substrates. Our fabricated devices show excellent control of the channel charge from the ferroelectric polarization. A clear memory behavior is demonstrated. We show that a pristine and smooth surface is critical to ferroelectric control; otherwise, the interface gets contaminated by surface charges, which completely screens out the polarization, leading to clockwise hysteresis loop. Our work may be useful for non-volatile memory devices and integrating amplifiers directly on functional ferroelectric and piezoelectric oxides. In addition, it may be possible to use the large polarization of a single crystalline ferroelectric oxide to electronically induce metal insulator phase transition. <sup>20–23</sup>

See supplementary material for the metallic state of  $MoS_2$  driven by positive polarization of the ferroelectric gate oxide layer.

This work was supported in part by the AFOSR Grant no: FA9550-13-l-0114 and the Center for Emergent Materials at the OSU, a NSF MRSEC center.

<sup>4</sup>S. Kim, A. Konar, W.-S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J.-B. Yoo, J.-Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi, and K. Kim, Nat. Commun. 3, 1011 (2012).

Y. Yoon, K. Ganapathi, and S. Salahuddin, Nano Lett. 11, 3768 (2011).

M. V. Strikha, JETP Lett. 95, 198 (2012).

<sup>7</sup>E. B. Song, B. Lian, S. Min Kim, S. Lee, T. K. Chung, M. Wang, C. Zeng, G. Xu, K. Wong, Y. Zhou, H. I. Rasool, D. H. Seo, H. J. Chung, J. Heo, S. Seo, and K. L. Wang, Appl. Phys. Lett. **99**, 042109 (2011).

<sup>8</sup>X. Hong, J. Hoffman, A. Posadas, K. Zou, C. H. Ahn, and J. Zhu, Appl. Phys. Lett. **97**, 033114 (2010).

<sup>9</sup>N. Park, H. Kang, J. Park, Y. Lee, Y. Yun, J. Lee, S. Lee, Y. H. Lee, and D. Suh, ACS Nano 9, 10729 (2015).

<sup>10</sup>H. S. Lee, S. W. Min, M. K. Park, Y. T. Lee, P. J. Jeon, J. H. Kim, S. Ryu, and S. Im, Small 8, 3111 (2012).

<sup>11</sup>C. Ko, Y. Lee, Y. Chen, J. Suh, D. Fu, A. Suslu, S. Lee, J. D. Clarkson, H. S. Choe, S. Tongay, R. Ramesh, and J. Wu, Adv. Mater. 28, 2923 (2016).

<sup>12</sup>F. A. McGuire, Z. Cheng, K. Price, and A. D. Franklin, Appl. Phys. Lett. 109, 093101 (2016).

<sup>13</sup>X. W. Zhang, D. Xie, J. L. Xu, Y. L. Sun, X. Li, C. Zhang, R. X. Dai, Y. F. Zhao, X. M. Li, X. Li, and H. W. Zhu, IEEE Electron Device Lett. 36, 784 (2015).

<sup>14</sup>A. Lipatov, P. Sharma, A. Gruverman, and A. Sinitskii, ACS Nano 9, 8089 (2015).

<sup>15</sup> A. Nguyen, P. Sharma, T. Scott, E. Preciado, V. Klee, D. Sun, I. H. Lu, D. Barroso, S. Kim, V. Y. Shur, A. R. Akhmatkhanov, A. Gruverman, L. Bartels, and P. A. Dowben, Nano Lett. 15, 3364 (2015).

<sup>16</sup>C. Zhou, X. Wang, S. Raju, Z. Lin, D. Villaroman, B. Huang, H. L.-W. Chan, M. Chan, and Y. Chai, Nanoscale 7, 8695 (2015).

<sup>17</sup>M. M. Benameur, B. Radisavljevic, J. S. Héron, S. Sahoo, H. Berger, and A. Kis, Nanotechnology 22, 125706 (2011).

<sup>18</sup>Y. Ye, Z. J. Wong, X. Lu, X. Ni, H. Zhu, X. Chen, Y. Wang, and X. Zhang, Nat. Photonics 9, 733 (2015).

<sup>19</sup>H. Qiu, L. Pan, Z. Yao, J. Li, Y. Shi, and X. Wang, Appl. Phys. Lett. **100**, 123104 (2012).

<sup>20</sup>B. W. H. Baugher, H. O. H. Churchill, Y. Yang, and P. Jarillo-herrero, Nano Lett. **13**, 4212–4216 (2013).

<sup>21</sup>X. Chen, Z. Wu, S. Xu, L. Wang, R. Huang, Y. Han, W. Ye, W. Xiong, T. Han, G. Long, Y. Wang, Y. He, Y. Cai, P. Sheng, and N. Wang, Nat. Commun. 6, 6088 (2015).

<sup>22</sup>B. Radisavljevic and A. Kis, Nat. Mater. **12**, 815 (2013).

<sup>&</sup>lt;sup>1</sup>G. H. Haertling, J. Am. Ceram. Soc. **82**, 797 (1999).

<sup>&</sup>lt;sup>2</sup>Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman, and M. S. Strano, Nat. Nanotechnol. 7, 699 (2012).

<sup>&</sup>lt;sup>3</sup>B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, Nat. Nanotechnol. **6**, 147 (2011).

<sup>&</sup>lt;sup>23</sup>J. T. Ye, Y. J. Zhang, R. Akashi, M. S. Bahramy, R. Arita, and Y. Iwasa, Science 338(80), 1193 (2012).